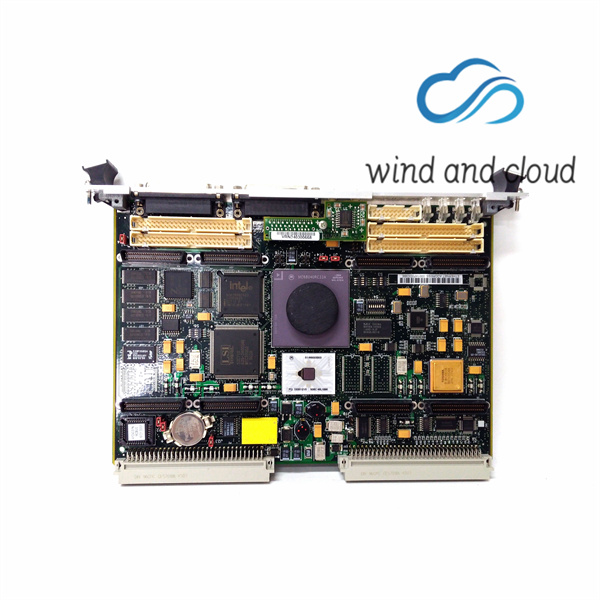

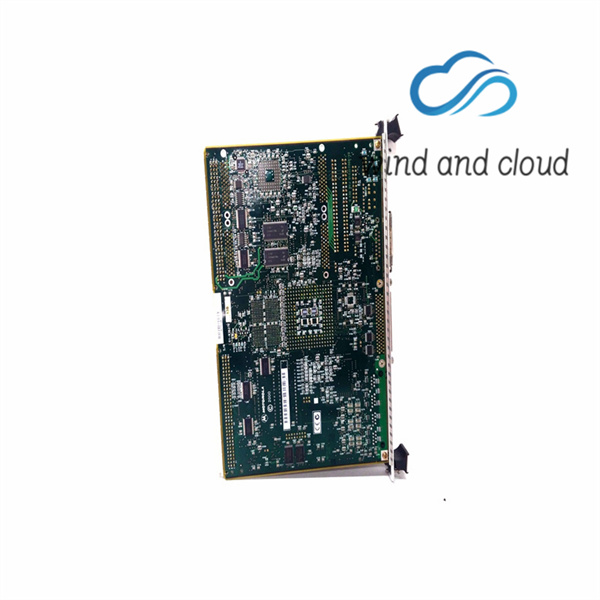

Register at address $FFF42048, bit 24. PROM/Flash is disabled at the low address space with PROM Control Register at address $FFF42040, bit 20. 2. This area is user-programmable. The DRAM and SRAM decoder is programmed in the MC2 chip, the local-to-VMEbus decoders are programmed in the VMEchip2, and the IP memory space is programmed in the IP2 chip. 3. Size is approximate. 4. Cache inhibit depends on devices in area mapped. 5.

The PROM and Flash are sized by the MC2 chip ASIC from an 8-bit private bus to the 32-bit MPU local bus. Because the device size is less than the allocated memory map size for some entries, the device contents repeat for those entries. If jumper GPI3 is installed, the Flash device is accessed. If GPI3 is not installed, the PROM is accessed. 6. The Flash and PROM are sized by the MC2 chip ASIC from an 8-bit private bus to the 32-bit MPU local bus. Because the device size is less than the allocated memory map size for some entries, the device contents repeat for those entries.

If jumper GPI3 is installed, the PROM is accessed. If GPI3 is not installed, the Flash device is accessed. 7. These areas are not decoded unless one of the programmable decoders are initialized to decode this space. If they are not decoded, an access to this address range will generate a local bus time-out. The local bus timer must be enabled.

There are no reviews yet.